1 min read

In theory, physical synthesis tools have all the necessary information about the layout; in practice, they must be correlated very carefully to real-world layout data.

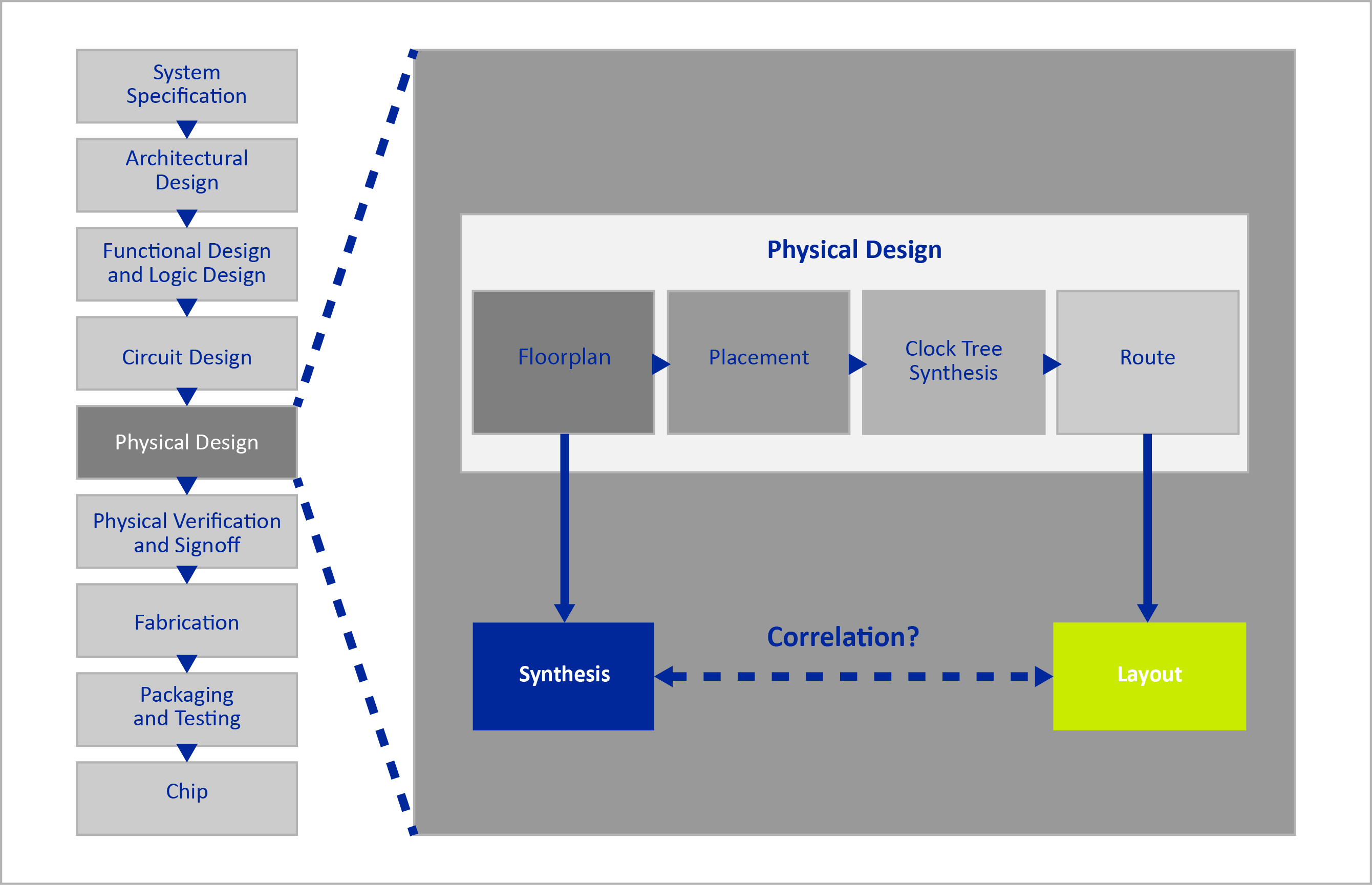

The design of a chip involves many stages, from system specification and architectural design, all the way to the fabrication and packaging of the final silicon that goes into a device. During this cycle, it is crucial to have reliable estimates of timing and area in order to plan properly and meet expectations.

Read the full article published on EETimes.

The Article will take a look into the physical design (or backend design) portion of the process; specifically, at the correlation of timing and area within the steps associated with the physical design.