- Solutions

- Products

- Resources

-

Company

Investor Relations

Investor RelationsFinancial Information

- Careers

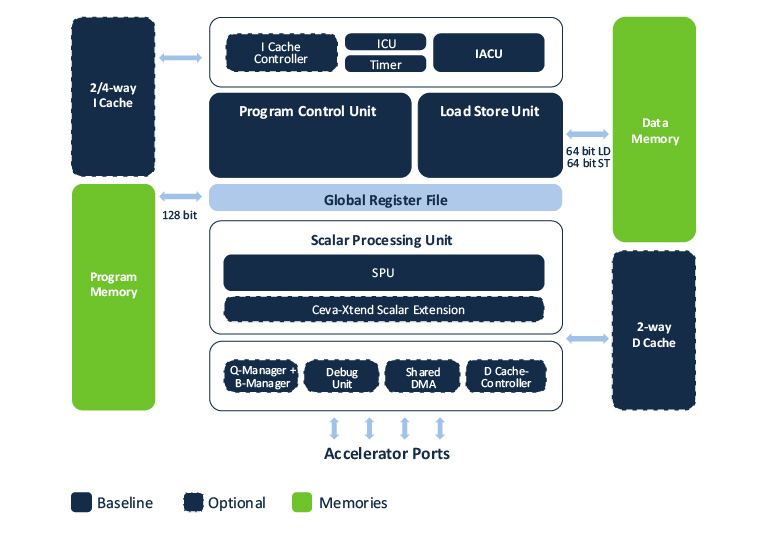

The Ceva-BX1 audio digital signal controller IP handles both modest signal-processing and control workloads with up to 8 GMACs per second performance and high-level-language programming. Yet it is power-efficient enough for always-on applications and use in wearables and TWS earbuds. The Ceva-BX1 supports a range of integer and floating-point data types for a wide range of applications, from audio signal processing to light AI workloads, with remarkably compact code size. Optimized high-speed interfaces expedite Ceva-BX1 connection to coprocessors or accelerators, and a rich software partners ecosystem provide ready-to-use application-level solutions.

Related Markets

The Solution

The Ceva-BX1 combines the capabilities of signal processing and control-code execution into a single compact, low-power DSP core. Computational speed comes from dual-32×32 and quad-16×16 MACs with added support for 16×8 and 8×8 MAC operations, implemented in an 11-stage pipeline. A floating-point unit supporting half, single, and double-precision IEEE floating-point is optional. These resources are directed by a four-way VLIW instruction set architecture with optimizations for single-instruction-multiple-data (SIMD) operation. A hardware loop buffer speeds kernel code execution, while efficient execution of control code is aided by dynamic branch prediction and a branch target buffer. Trusted execution modes enable secure operation. On signal-processing tasks the Ceva-BX1 can reach up to 8 GMACs per second, and on control workloads it can achieve up to 4.41 CoreMark/MHz. The hardware design is optimized for speed, achieving 2 GHz operation when implemented in a TSMC 7nm process node using only common standard cells and memory compilers.

Benefits

The Ceva-BX1 delivers the capabilities of both a compact audio DSP core and a capable MCU to power-constrained environments, handling both signal-processing and control workloads in a single core. DSP performance is sufficient for multi-microphone environmental noise cancellation, light AI processing, and high-accuracy sensor fusion, for examples. High-speed ports with automatic queuing and buffer controls make it easy to attach coprocessors and accelerators with the DSP. With a hardware design optimized for very low power and high speed, the performance of the Ceva-BX1 can be achieved without assembly-coding, using only C/C++ code generated by an LLVM compiler. The compiler, an RTOS, an Eclipse-based tool chain, extensive libraries for DSP and neural-network operations, and support for neural-network frameworks are all provided.

Key Features

- 4-way VLIW architecture with dual 32×32 or quad 16×16 MACs and optional half/single/double-precision IEEE floating-point unit

- Support for 8, 16, 32, and 64-bit integer operations, including 16×8 and 8×8 MAC operations for neural-network computations

- Sophisticated optimizations for control flow, including hardware loop buffer, branch target buffer, and dynamic branch prediction

- Trusted execution modes for secure operation

- Performance up to 8 GMACs per second and 4.41 CoreMark/MHz

- Hardware provisions for attaching coprocessors and accelerators

- Supported by LLVM compiler, Eclipse debug environment, and extensive libraries