- Solutions

- Products

- Resources

-

Company

Investor Relations

Investor RelationsFinancial Information

- Careers

Open RAN Platform for 5G Infrastructure

Ceva-PentaG RAN

Open-RAN and Massive MIMO devices." data-requestedassetproductmkto="Ceva-PentaG RAN" >Download Product Note

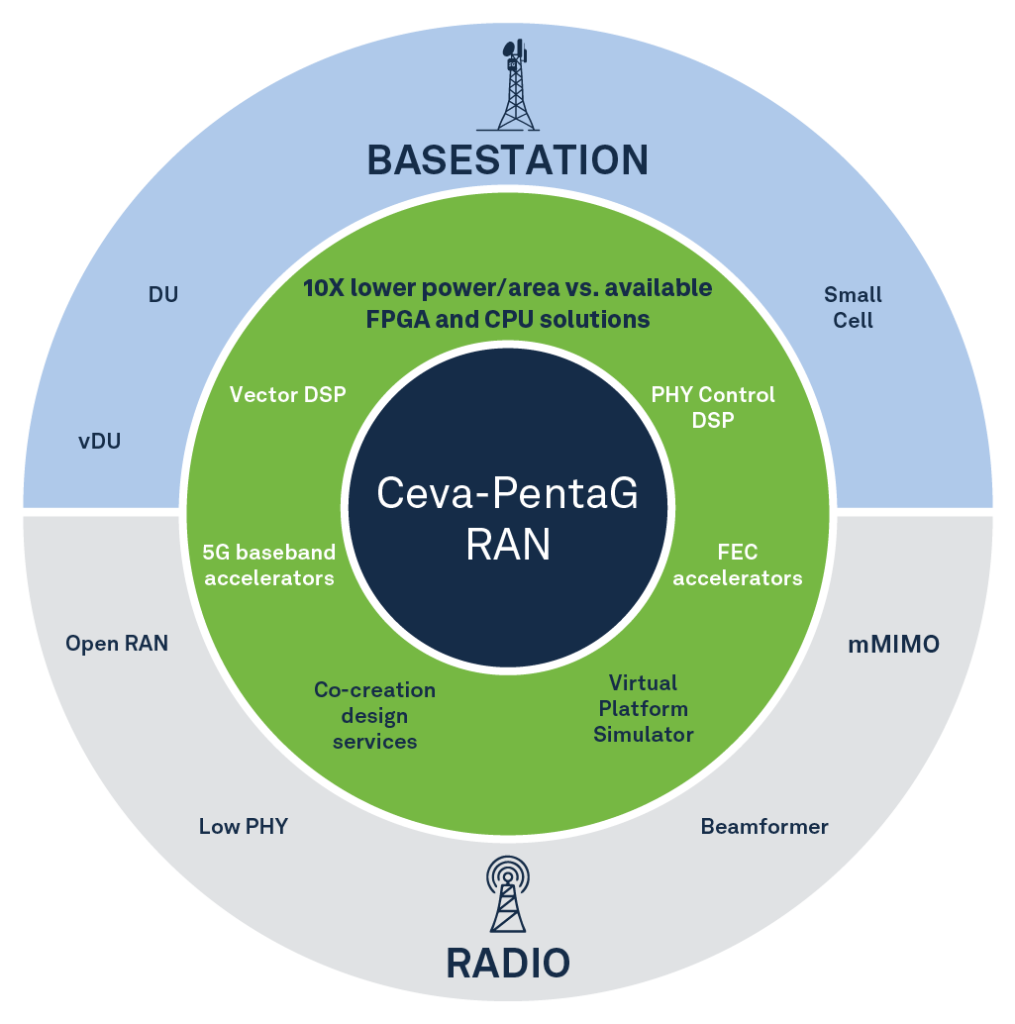

The Ceva-PentaG RAN platform is a modular, optimized hardware and software IP for implementing L1 PHY baseband processing in 5G base station and other cellular infrastructure SoCs. Employing Ceva’s highest-performance DSP cores and dedicated hardware accelerators teamed with optimized software, the Ceva-PentaG RAN platform is in use by 5G industry incumbents, and can substantially reduce development time and risk for new entrants. Highly scalable, it provides high-performance processing for all major signal and control chains for macro cell base stations, small cells, and remote radio units, supporting any Open-RAN high-PHY/low-PHY split. Special attention is given to massive MIMO, beamforming, and the specific needs of non-terrestrial network (NTN) gateways and satellites.

Related Markets

The Solution

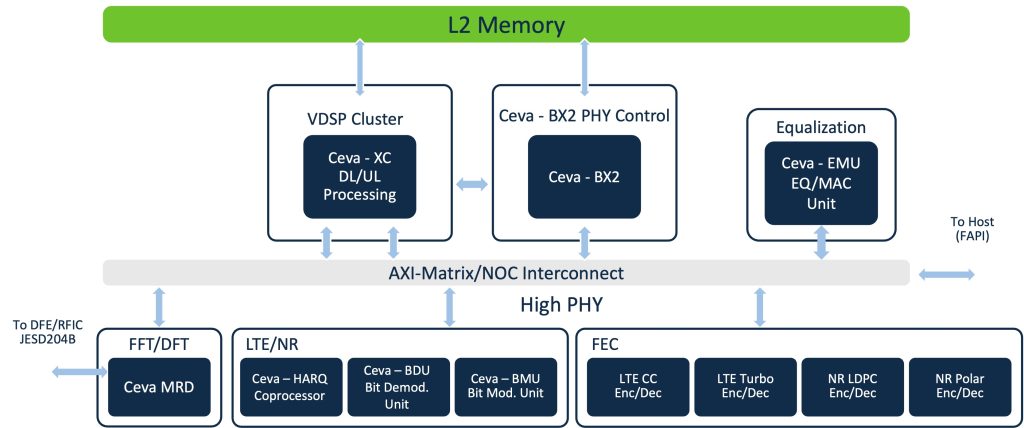

The Ceva-PentaG RAN platform comprises both hardware IP – Ceva-XC22 vector DSP cores, optimized accelerators, and supporting software, all with proven interoperability. Blocks support processing for each signal and control chain in the user’s application. This approach yields unmatched power-performance-area figures of merit for completed designs.

For base-station SoCs, all main signal and control chains are supported, including frequency-domain chains such as FFTs and equalization, symbol/bit-domain tasks including forward error correction, massive MIMO processing and beamforming, and Open-RAN fronthaul/backhaul processing. Modules can be assembled to create optimal hardware across a wide range of configurations from massive MIMO macro cell base stations to small cells.

5G / 5G-Advanced gNB RAN Blueprint Design by Arm, Ceva and SynaXG

This solution is created in collaboration with Arm, Ceva and SynaXG to redefine energy-efficient 5G NR Processing for sustainable LEO Satellites and 5G-advanced wireless infrastructure. Read more about it here

Benefits

With a complete hardware and software baseband platform for 5G infrastructure, the Ceva-PentaG RAN provides SoC developers, whether incumbent or entering, with a way to slash development time and risk. Based on the Ceva-XC22 DSP core – with the industry’s best power, performance, and area – and on highly optimized dedicated accelerator IP blocks, Ceva-PentaG RAN provides the components for building market-leading SoCs across a wide range of performance and cost points, from the most complex massive MIMO base stations to new NTN gateways and satellite payloads to the most efficient 4×4 MIMO small cells.

To speed development and ensure design quality from the very beginning of the design cycle, the full Ceva-PentaG RAN platform is supported in Ceva’s System-C modeling environment, the Virtual Platform Simulator (VPS). There is an FPGA emulation for real-time debug.

Key Features

- Optimized and proven hardware IP including Ceva-XC22 vector DSP and Ceva-BX controller DSP cores

- Optimized dedicated hardware accelerators for specific processing chains

- Support for massive MIMO up to and beyond 64TR with beamforming

- Vector DSP acceleration for channel estimation and MMSE computation

- Support for NTN gateways and orbital payloads

- Full simulation in Ceva Virtual Platform Simulator System-C environment

- Hardware FPGA emulation