Scalable Audio Processing DSP Architecture for High-Performance, Low-Power Audio, Voice, and Speech

The CEVA-TeakLite 4™ is the most advanced member of the CEVA TeakLite® DSP family, designed for efficient audio processing in high-volume, cost-sensitive applications. Founded on an efficient memory-based architecture, the CEVA TeakLite family combines small die size and high code density with high levels of audio processing power.

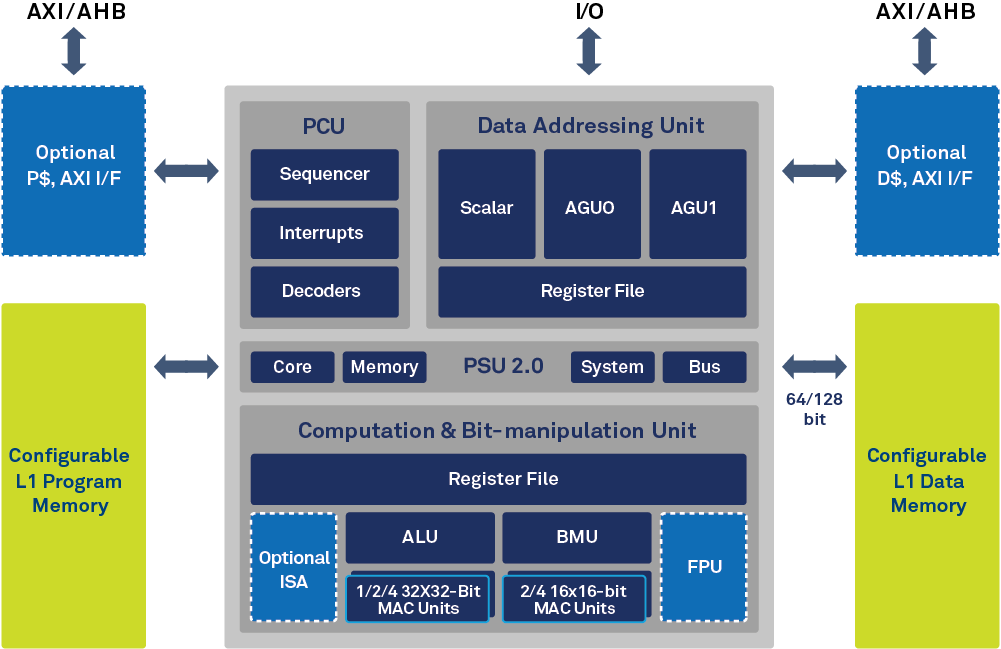

Based on a native 32-bit architecture, different members of the CEVA-TeakLite family can perform one, two, or four 32×32-bit Multiply-Accumulate (MAC) operations, as well as two or four 16×16-bit MAC operations in a single cycle. These scalable options enable a precise balance to optimally address different target applications, like baseband audio and voice, media codecs, voice-activated interfaces and more.

The CEVA-TeakLite 4 architecture supports both an advanced set of digital signal audio processing instructions as well as general-purpose microprocessor instructions. The instruction set and programming model are designed for straightforward generation of compact and efficient code and the integrated second-generation Power Scaling Unit (PSU 2.0) minimizes power consumption via advanced power management (including support for clock and voltage scaling).

All members of the CEVA TeakLite family are compatible with each other and are backward compatible with their predecessors, including the widely adopted TeakLite®, CEVA-TeakLite II™, and CEVA-TeakLite III™ DSP cores. This enables new audio DSP chip designs to leverage existing applications and a large installed base of software and simplifies the migration of existing designs to a higher performance DSP core.

Benefits

The integrated, high-performance, ultra-low-power CEVA-TeakLite-4 family enables rapid design of DSP-based solutions for audio, voice, and speech applications.

Main Features

- Enhanced bit-manipulation capabilities for efficient stream processing

- Up to 5 operations executed in parallel

- Dedicated single-precision and double-precision FFT instructions

- Up to 4 GW program memory and 4 GW data memory (16-bit words)

- L1 program memory (TCM or 4-way cache)

- L1 data memory (TCM or 2-way, set-associative, hardware-configurable cache)

- Optional floating-point unit

Block Diagram

Wireless headset technologies and trends

CEVA and Silentium have partnered to drive these trends with DSP and software ANC technologies which can be easily and quickly configured and ported to SoC designs. In this webinar, we depict a holistic wireless sound solution based on CEVA’s audio DSP and Silentium’s software-based ANC application targeting cost and power sensitive wireless headsets and earbuds.