Overview

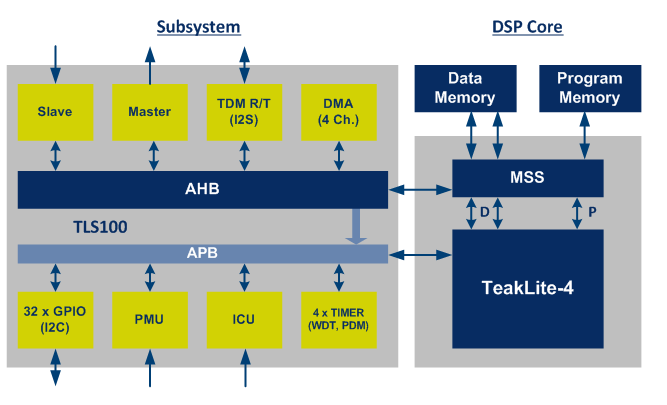

The CEVA-TLS100™ is a fully-featured integrated subsystem that includes all main system peripherals and interfaces and seamlessly connects to the CEVA audio and sensing solutions.

The multi-layer AHB-lite bus architecture comprises two main modules; the Master Interface Module (MIM) decodes addresses and negotiates with the slave while the Slave Interface Module (SIM) arbitrates between the masters and responds to requests. Equipped with 64-bit bandwidth, the CEVA-TLS100 is able to connect to 32-bit systems while operating at half of the DSP core frequency.

The on-board DMA controller has 4 channels supporting flexible and powerful DMA transfers including a specialized 3D DMA transfer for video/audio processing. The hardware DMA manager can be pre-configured and free up the DSP core.

The subsystem also includes a buffered time division multiplexing (TDM) port with 8-stage 32-bit receive and transmit FIFO buffers. The AHB-to-APB bridge converts APB, AHB or DMA transactions into APB thus enabling the connection of low-speed peripherals including ICU, PMU, Timers and GPIO on APB BUS.

Four 32-bit timer/counters allow for 4-bit pre-scaling and the generation of PWM drive signals. Can be used as watch dog timer. working from either an internal or external clock source.

The Power Management Unit (PMU) controls all system clock and reset signals allowing for selective event-based wakeup and further reducing power by stopping clocks when not required.

Benefits

The CEVA-TLS100 subsystem provides all necessary peripherals and interfaces for simple and rapid development of more complex systems based on the CEVA audio and sensing DSP cores.

Main Features

- A rich set of peripherals and interfaces

- 4 channel DMA controller

- Minimal gate count

Block Diagram