Overview

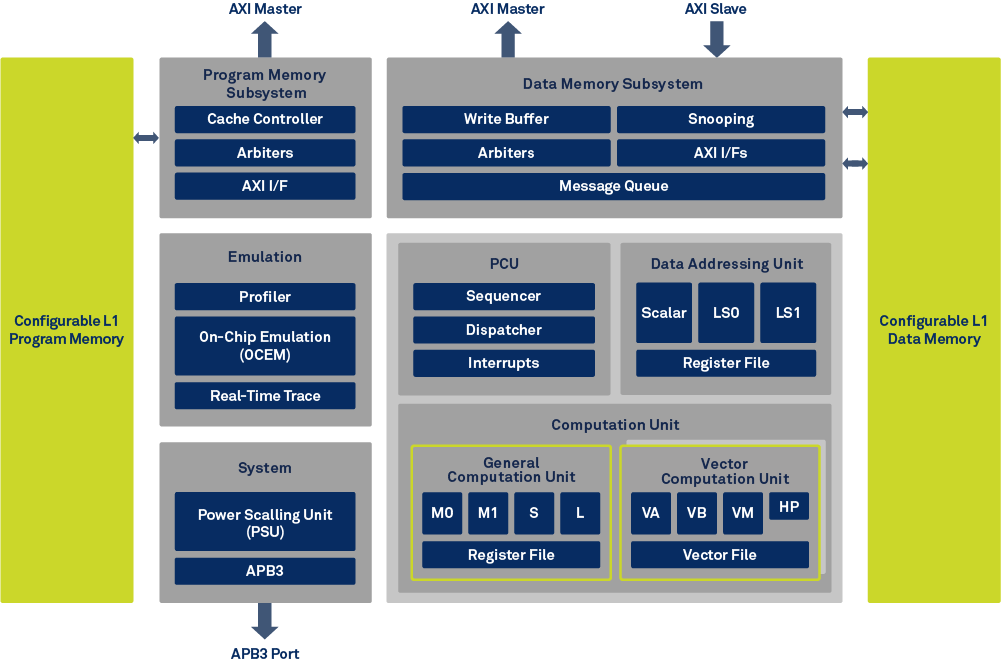

The CEVA-XC323 is the fifth generation of the widely deployed CEVA-XC architecture, and is optimized for IoT communication applications as well as cellular UE and wireless and wireline terminals. The CEVA-XC323 delivers powerful vector capabilities with a general computation engine to supply the extreme performance and flexibility demanded by a wide variety of IoT communication applications.

Based around a fully programmable DSP processor architecture, the CEVA-XC323 offers a wealth of features, including two vector processing units (VPUs). Each VPU provides a powerful SIMD engine that allows for eight simultaneous VLIW instructions. The processing units give efficient DSP support for non-vector data as well as for control and ANSI-C operations.

Extremely powerful computation capabilities include 32 16×16-bit MAC operations with 64-bit arithmetic operations, or more than 200 16-bit operations, per cycle.

The integrated solution offers a complete memory subsystem with Tightly Coupled Memories (TCM), caches, AXI and APB interfaces, and an advanced DMA controller. These ensure easy integration and optimal performance in target SoCs.

Exceptional power efficiency is provided by the embedded Power Scaling Unit (PSU 2.0), the power-optimized Tightly Coupled Extensions (TCEs), and an enhanced power-optimized pipeline.

Benefits

The CEVA-XC323 scalable multi-mode communication processor for IoT wireless applications delivers highly powerful vector capabilities alongside a general computation engine giving extreme performance and flexibility.

Main Features

- Fully programmable DSP processor architecture

- Complete memory subsystem with instruction cache

- Integrated PSU

- Instruction set optimized for OFDMA processing

Block Diagram